検証環境構築効率化ツール「Log2SVA+」

●SVAを用いた検証環境を効率良く作成したいと思いませんか?●

SystemVerilogの普及に伴い、複雑な検証環境が比較的容易に作りやすくなってきました。

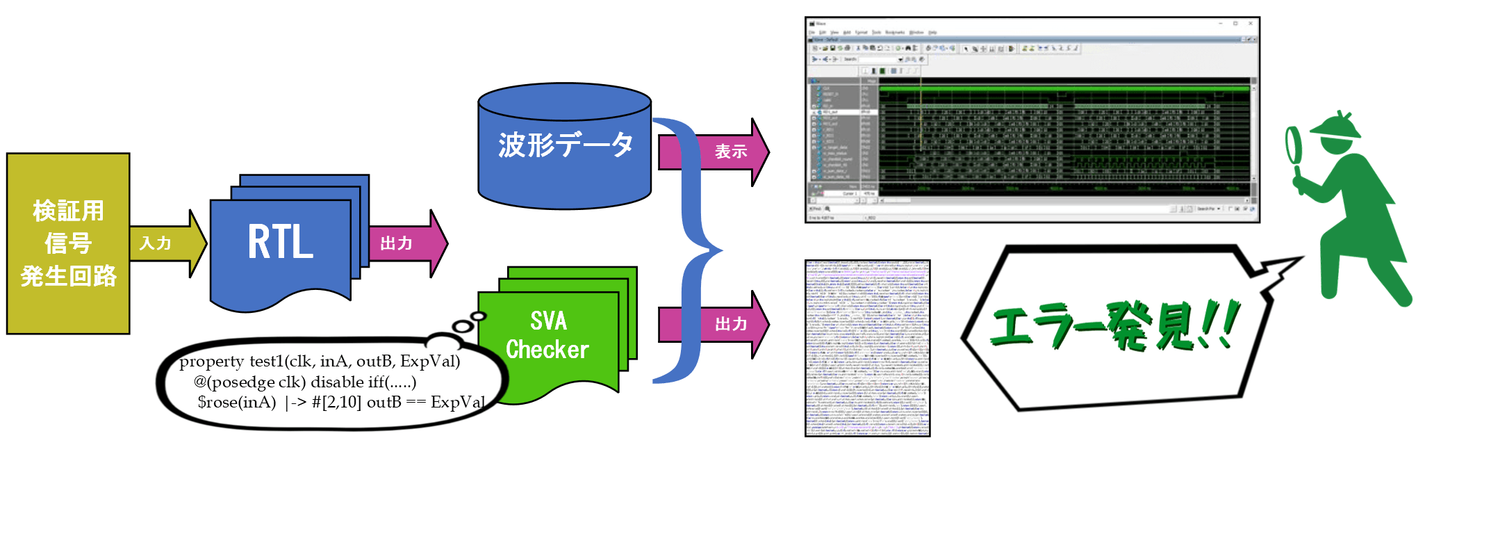

なかでも、SVA(=SystemVerilogAssertion)を活用することで、

検証の網羅性(機能カバレッジ)が視覚化しやすくなってきたと思います。

本ツールは、SVAを用いた検証環境を効率良く作成することを支援するツールです。

是非、どのようなものなのか体験してみてください。

なかでも、SVA(=SystemVerilogAssertion)を活用することで、

検証の網羅性(機能カバレッジ)が視覚化しやすくなってきたと思います。

本ツールは、SVAを用いた検証環境を効率良く作成することを支援するツールです。

是非、どのようなものなのか体験してみてください。

SVAを用いたCheckerはテストベンチを不要とするフォーマル検証にも使えたり、

ブロックでもチップ環境でも使えたり、メリットが沢山あります。

しかしながら、

SVAの言語を覚えたり、効果的なSVAを作成できるようになるまで、少し、時間を必要とします。

また、FPGAで開発している場合、

RTL Simulation工数をできるだけ短手番で済ませたい場合もあります。

そんな時に弊社のこのツールを使って効率良く、SVAによるCheckerをを作成しませんか?

ブロックでもチップ環境でも使えたり、メリットが沢山あります。

しかしながら、

SVAの言語を覚えたり、効果的なSVAを作成できるようになるまで、少し、時間を必要とします。

また、FPGAで開発している場合、

RTL Simulation工数をできるだけ短手番で済ませたい場合もあります。

そんな時に弊社のこのツールを使って効率良く、SVAによるCheckerをを作成しませんか?

みなさん!このツールを、是非、活用してみませんか?

「log2sva_contact@axsl.co.jp」に問い合わせてください。

「log2sva_contact@axsl.co.jp」に問い合わせてください。

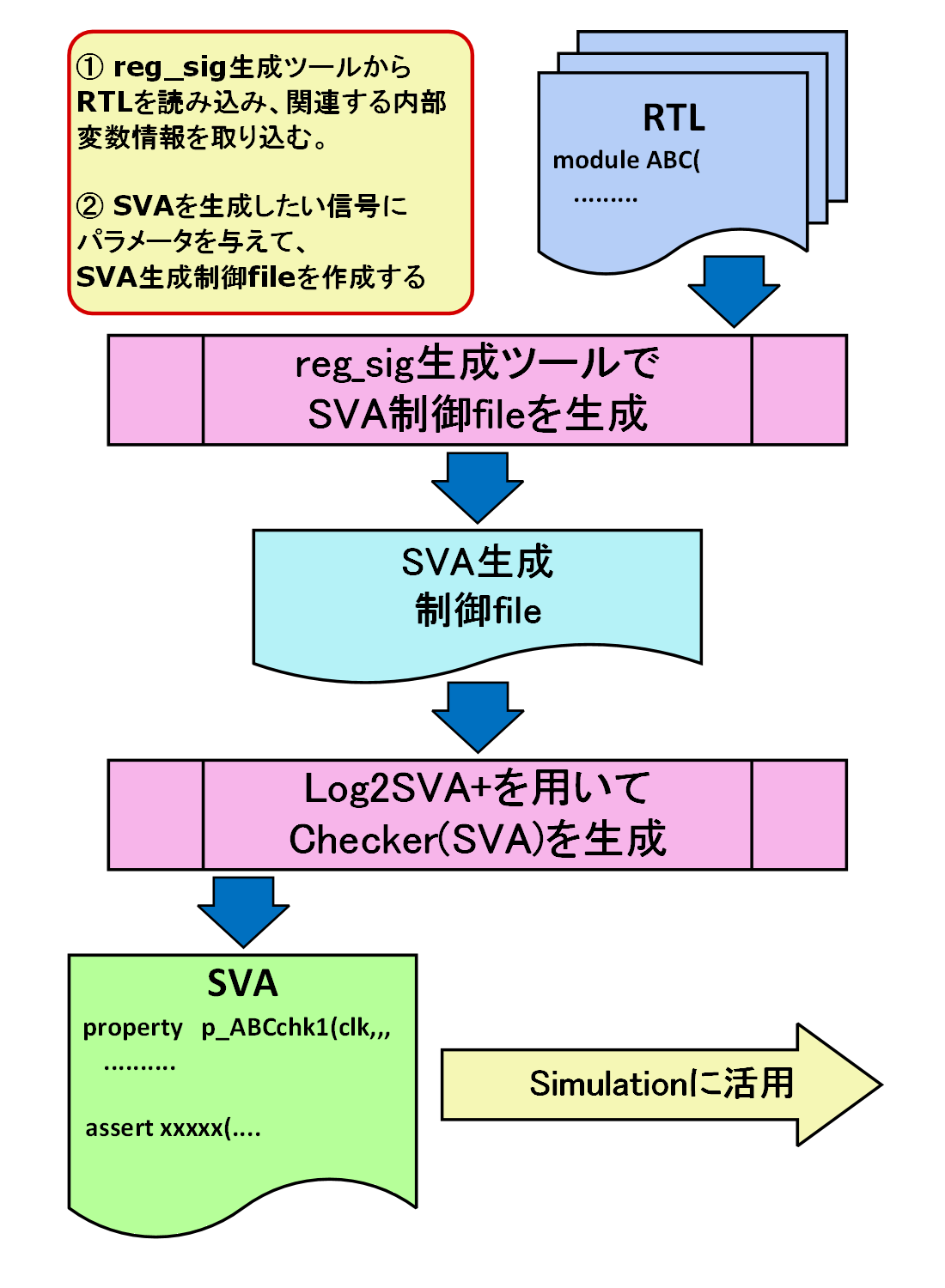

★Log2SVAの使い方★

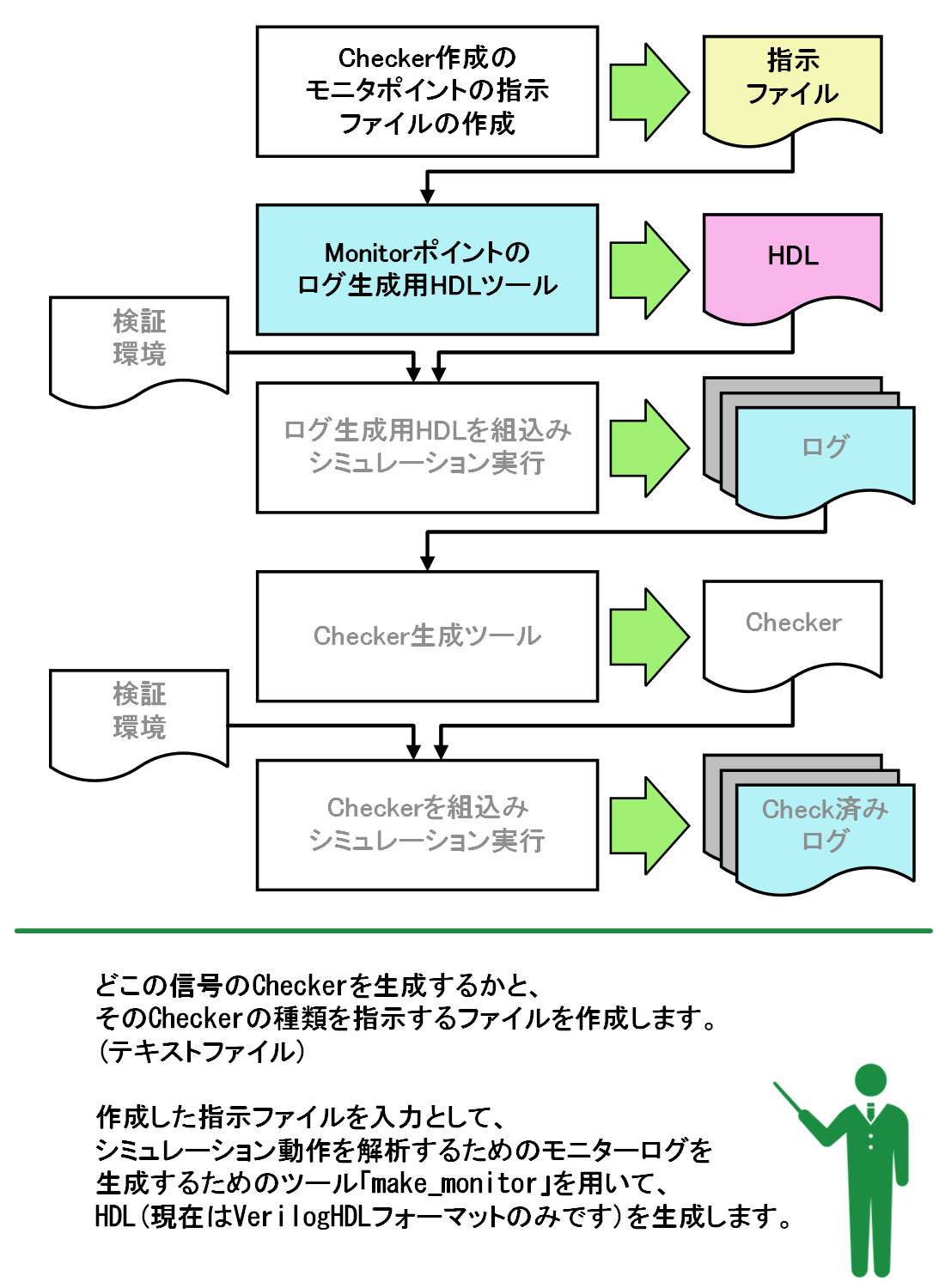

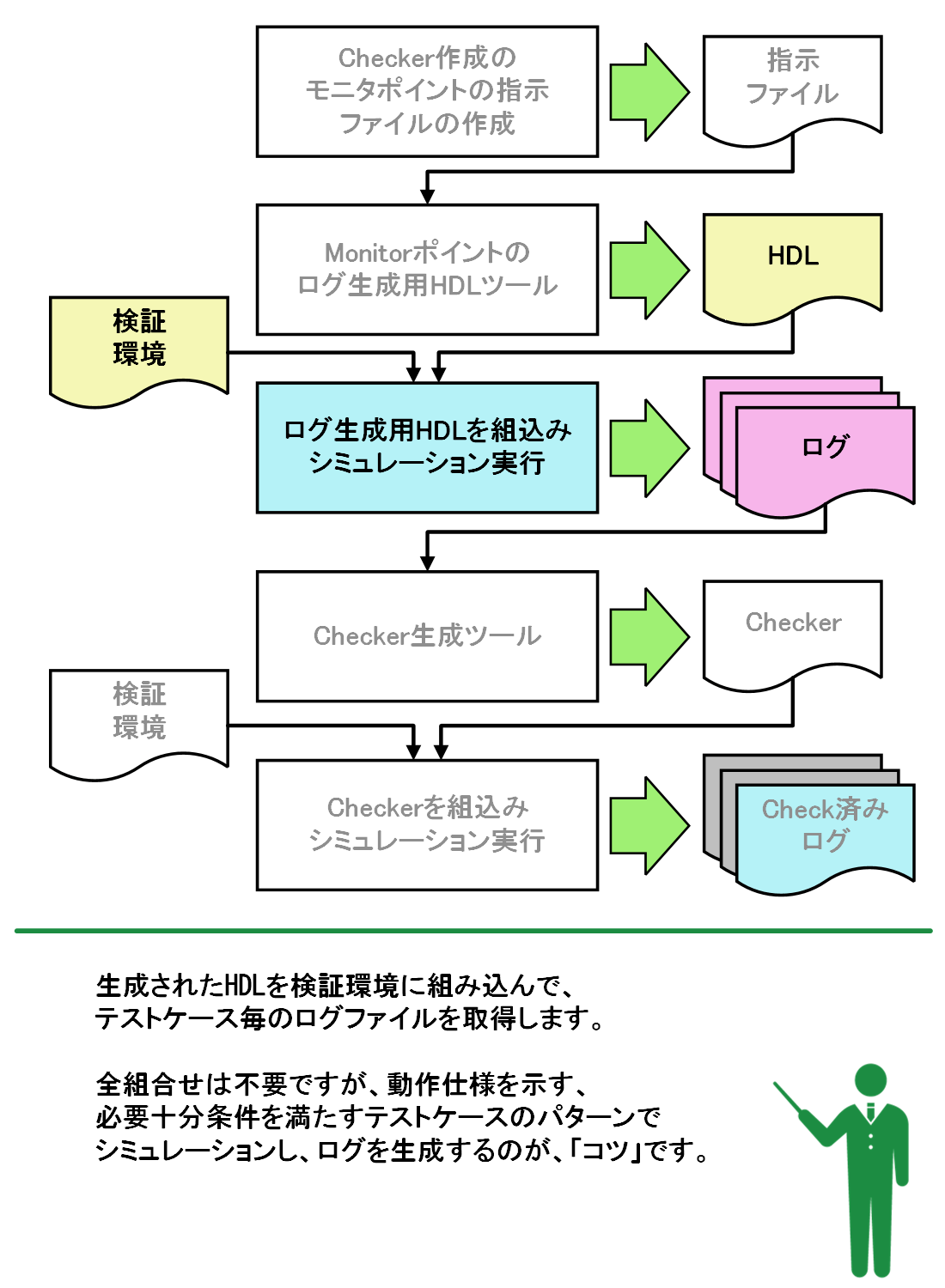

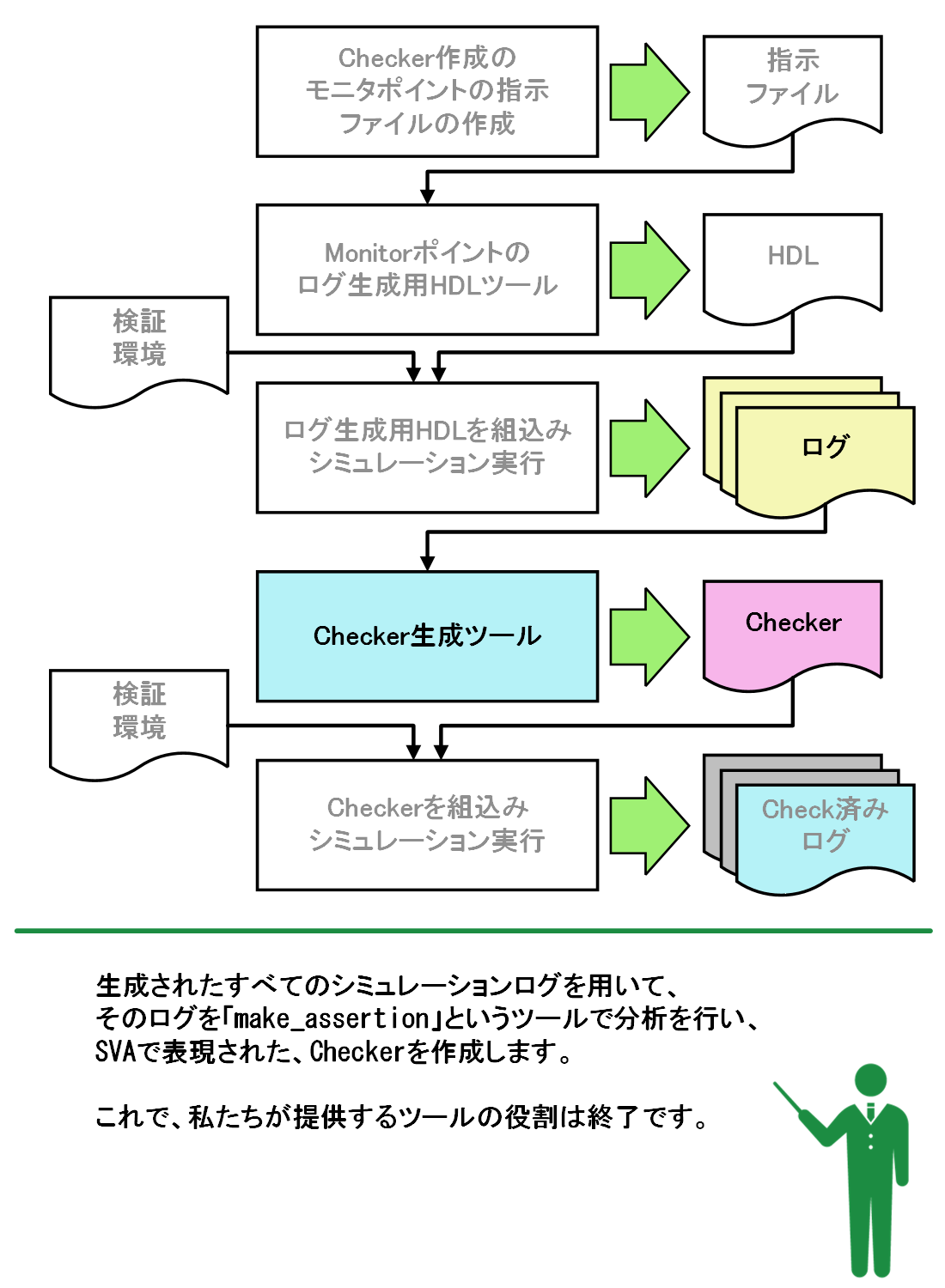

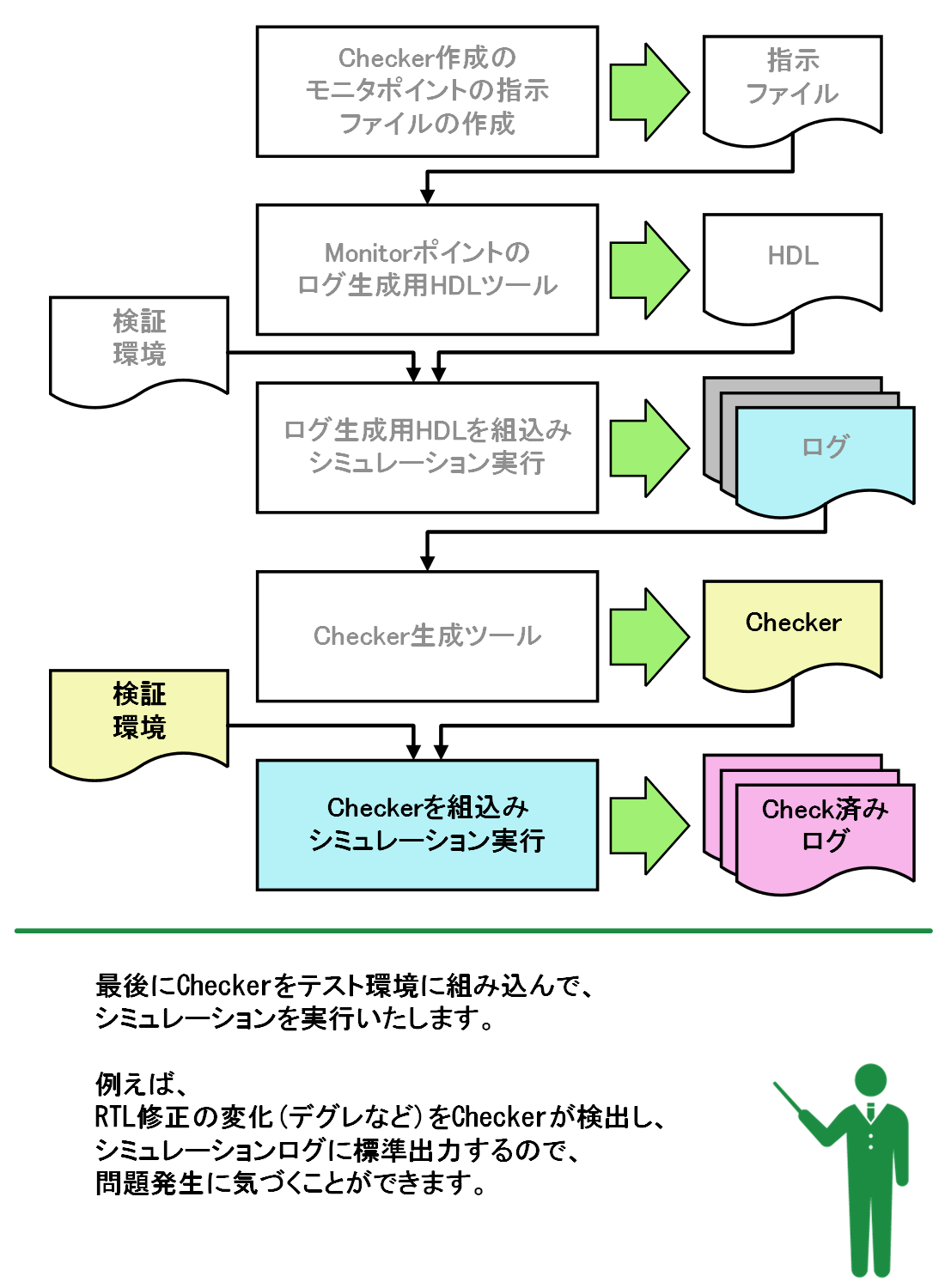

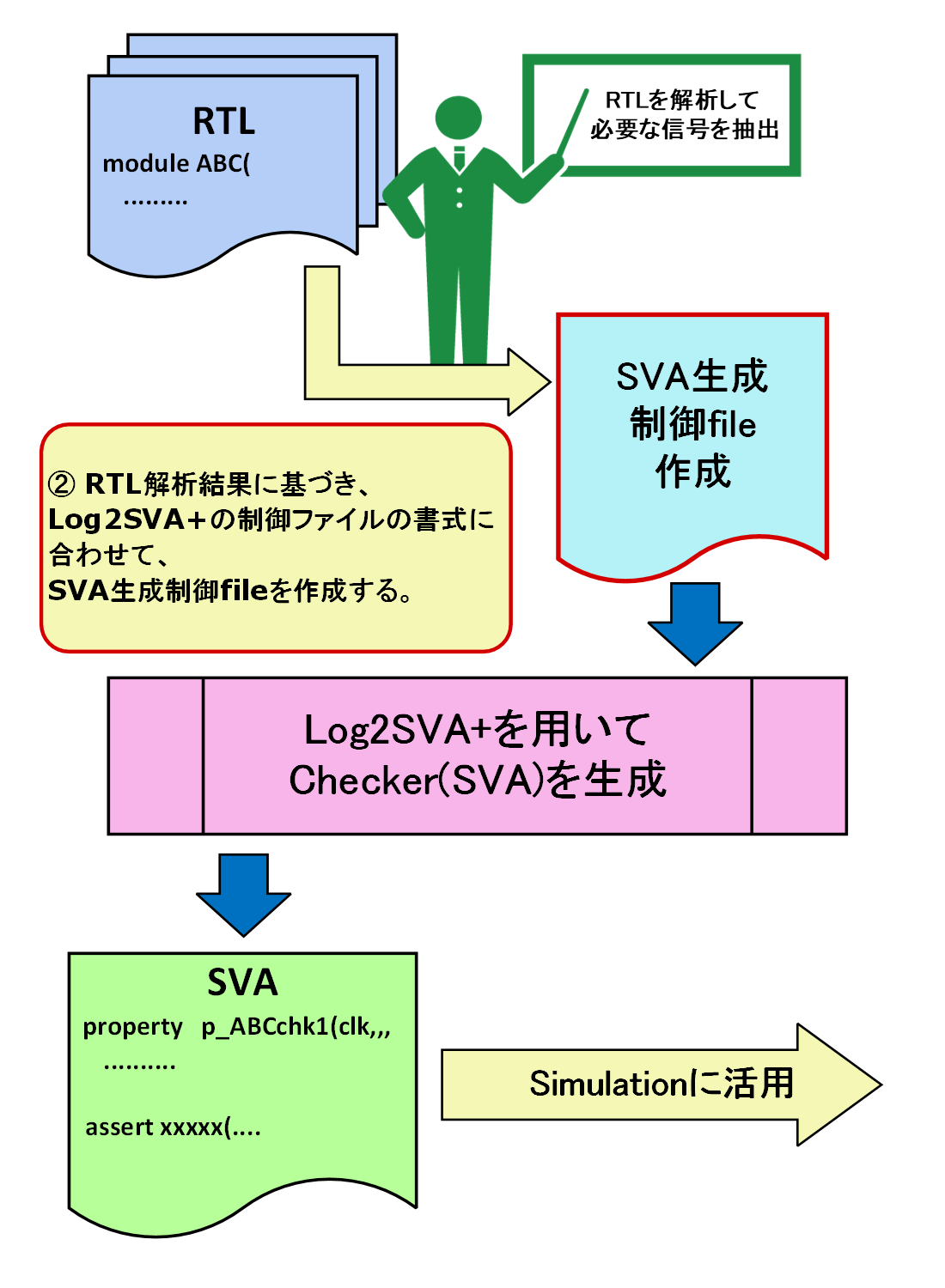

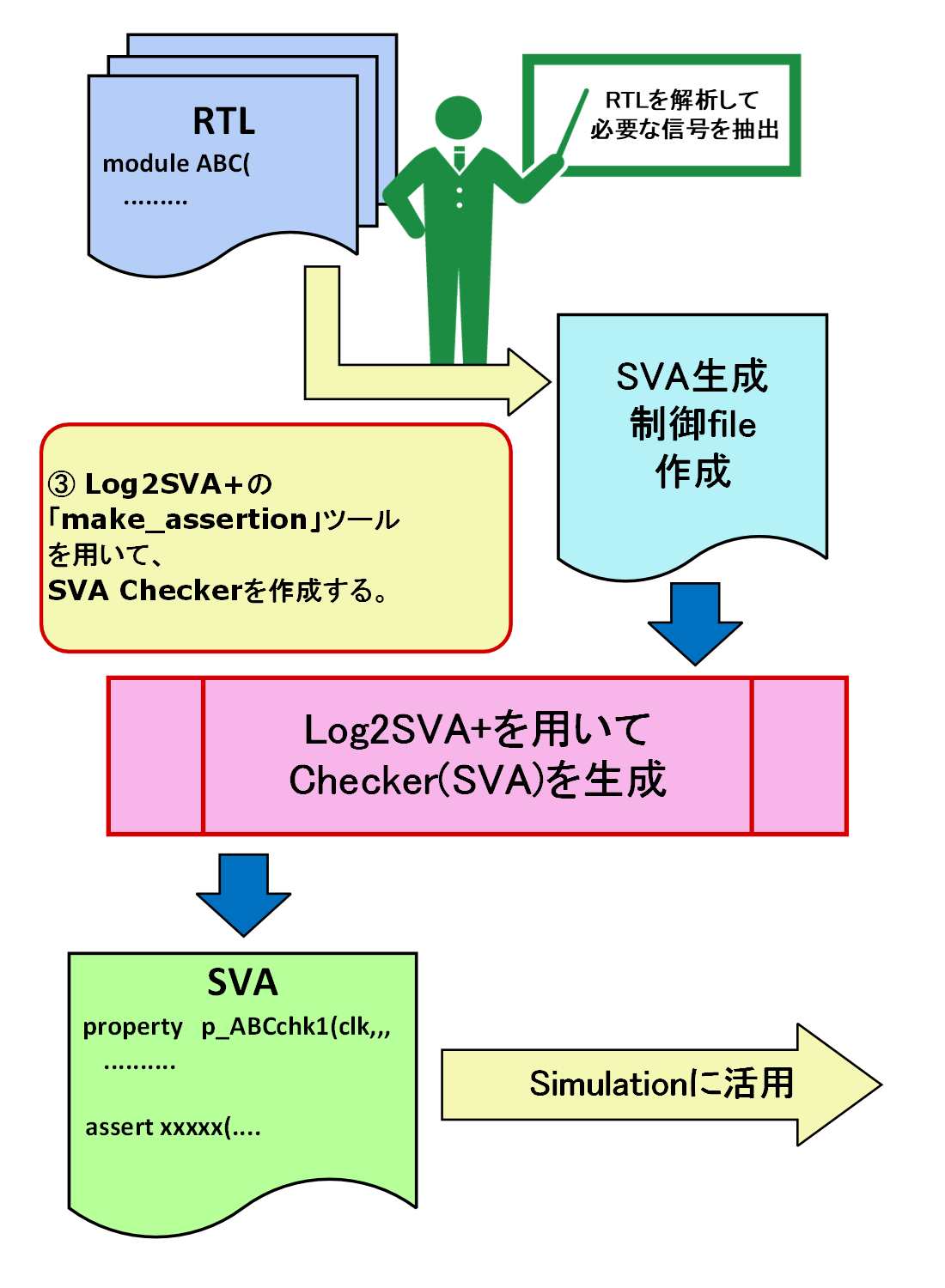

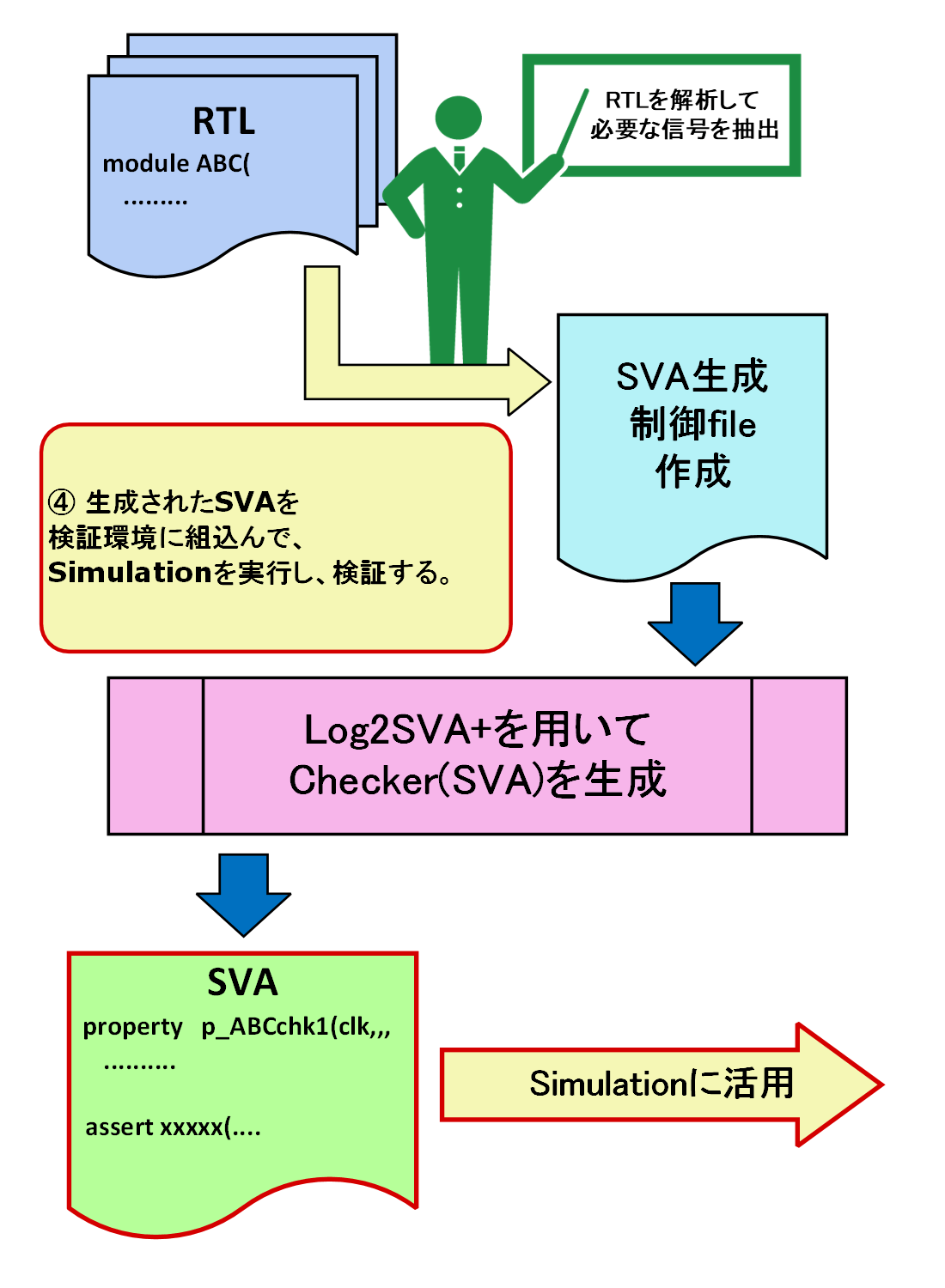

以下の3つの場合について、簡単に説明します。①シミュレーションを流して作成する方法

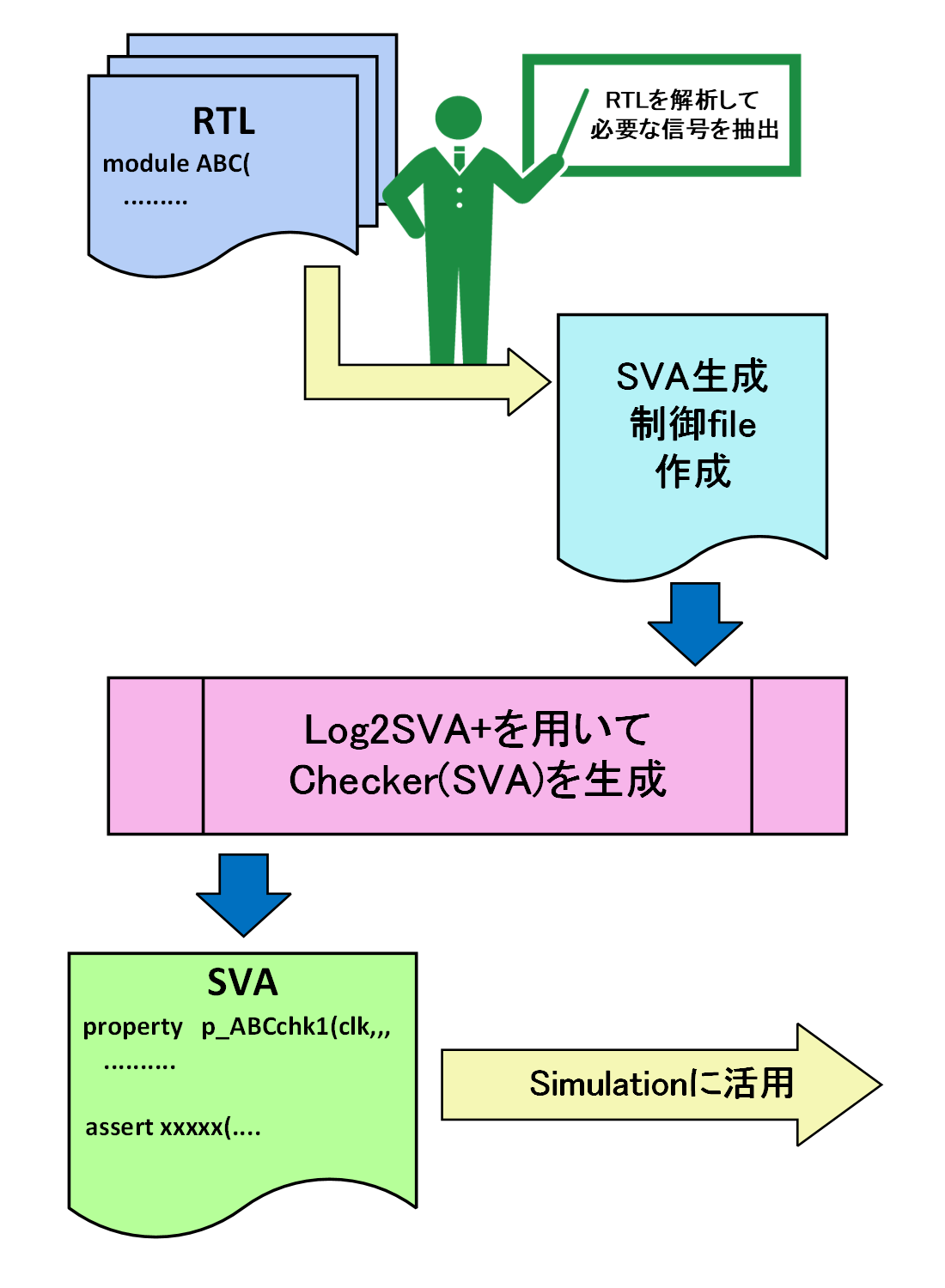

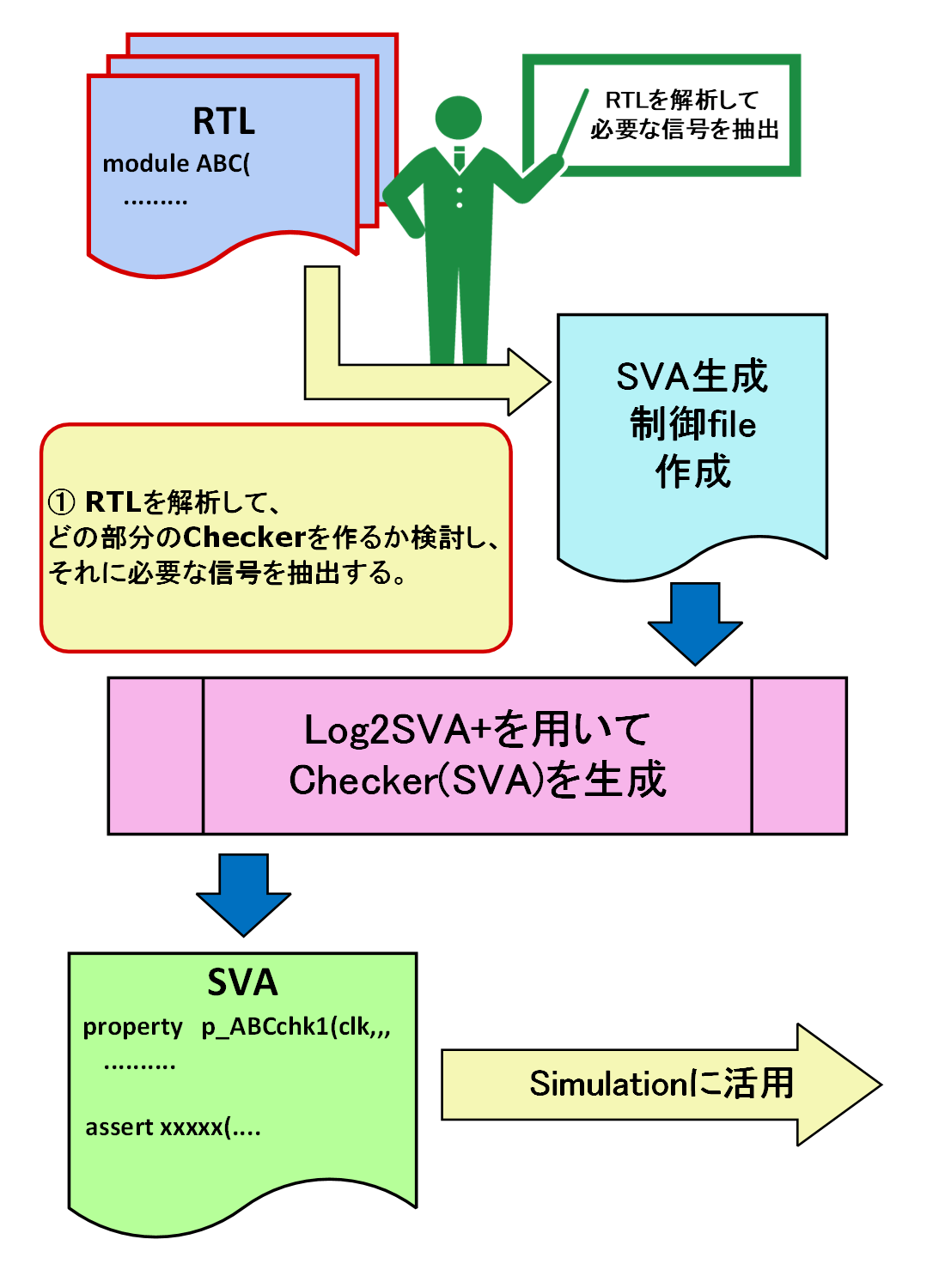

②制御ファイルから直接作成する方法

③制御ファイルを用意に作成する方法

Log2SVA+のツール概要

| 簡単に言うと | SVAを用いたRTL検証用Chekcerを容易に生成するツール |

|---|---|

| 動作環境 |

Windows10(64bit)以降のOS。 ※Linuxサポートは検討中です。 また、生成されたSVAはOSに依存しません。 (日本語等は影響あり) |

| サポート言語 |

VerilogHDLのみ ※SystemVerilog, VHDL版のサポートは検討中です。 |

| ツールの種類 |

・SVAの元データを Simulationのlog経由で作成するためのHDL生成ツール ・SVAを作成するツール ・SVA作成のための 制御ファイルを作成するための補助ツール |

| ツール概要 |

・make_monitor : Simulationを流し、SVAの期待値となる Logを作成するためのHDL生成ツール。 ・make_assertion : SVA生成のための制御ファイル またはSimulationログからSVAを生成するツール ・reg_sig生成ツール : RTLを読み込み、ブロック単位で SVA生成のための制御ファイルを作成するツール ブロック単位のものをChip全体に集約もできます。 |

| 生成できるチェック (SVA)機能 |

以下に示す11機能に、 更にオプションでチェック条件を変更可能 ①リセット関係チェック ②信号の取りうる範囲のチェック ③FSMのチェック ④2地点間の接続チェック ⑤2つの信号の関係性チェック ⑥パルスチェック ⑦グレイコードチェック ⑧パリティエンコードチェック ⑨デコードチェック ⑩丸め処理チェック ⑪微分信号チェック |

| 販売形態および費用 |

保守込みで1年契約となります。 費用はlog2sva_contact@axsl.co.jpを用い、 営業担当に お問合せください。 |

| 評価(体験)について |

常時受け付けています。 log2sva_contact@axsl.co.jpに 「評価希望」と記載の上 会社(または学校)名および、 評価に用いるパソコンのMacアドレス情報も併せてご連絡ください。 評価期間は原則2週間です。 なお、評価完了後(ライセンス有効期限後)、 簡単なアンケートのご協力をお願い致します。 ★ご評価の際は、NDAの締結が必要になります。★ |

| ライセンス |

ノードロックのライセンス形態になります。 マシン1台に付き、無期限相当(100年)の有効期間で発行します。 ご注文の際は、購入ライセンス分のマシンのHostID(Macアドレス)を ご連絡お願い致します。 |

| 問い合わせ先 |

宛先: 販売関係 : 管理部)営業課 埴原、池亀 技術関係 : ハードウェア技術部)ASG 金子 TEL 045-306-9075 メールアドレス : log2sva_contact@axsl.co.jp |

| その他、ご連絡事項 |

・ご質問、デモ実施等のご希望等は、 log2sva_contact@axsl.co.jpよりお問合せください。 |